|

| Tί είναι τελικώς το

Jitter; |

|

1. Ο ορισμός του Jitter - Δείγματα και μπαλάκια του

τένις...

2. Πόσα είδη Jitter

υπάρχουν;

3. Μπορούμε να μετρήσουμε, να

ακούσουμε και να μειώσουμε το Jitter;

4. H ανάκτηση του σήματος χρονισμού (clock

recovery) και το PLL

5. Για περισσότερο

Διάβασμα... |

|

|

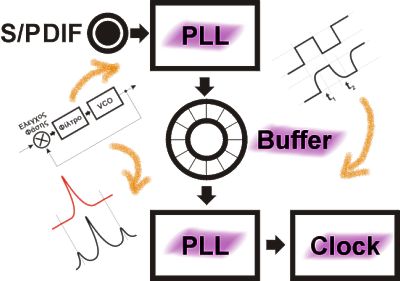

| Η λογική λέει ότι αν έχετε

φτάσει μέχρι αυτό το σημείο του κειμένου θα έχετε -σχεδόν-

απογοητευθεί. Από τις περιγραφές, μπορεί κανείς να αντιληφθεί

ότι το jitter δεν αποφεύγεται, είμαστε μάλιστα τυχεροί αν δεν

περιλαμβάνεται και στον ίδιο τον δίσκο, λόγω μιας μέτριας

διαδικασίας ψηφιοποίησης. Υπάρχουν τριών ειδών jitter τα οποία

μετέχουν ταυτόχρονα και σε άγνωστους σε εμάς συνδυασμούς σε ένα

τελικό αποτέλεσμα: Τα σημεία του ψηφιακού σήματος που χρησιμοποιούμε

για να συγχρονίσουμε τα επιμέρους τμήματα ενός ψηφιακού συστήματος

αναπαραγωγής είναι ασαφώς κατανεμημένα χρονικά. Είναι αλήθεια ότι αν

βασιστούμε στο ψηφιακό σήμα, ως έχει, για τον συγχρονισμό του

συστήματος, το αποτέλεσμα θα είναι μάλλον αρνητικό (δηλαδή, δεν θα

δουλεύει τίποτε). Στην πράξη, όμως, έχουμε στην διάθεσή μας

μία σειρά από τεχνικές που μας επιτρέπουν όχι να "εξάγουμε"

το clock από ένα παραμορφωμένο σήμα αλλά να το ξαναδημιουργήσουμε.

Οι τεχνικές αυτές είναι γνωστές ως clock recovery

και παρά το γεγονός ότι θα τις συναντήσετε με διάφορες ονομασίες και

περιγραφές (περισσότερο ή λιγότερο προσγειωμένες και ακριβείς...)

είναι στην πράξη, τρείς: Το PLL, το διπλό

PLL και το διπλό PLL με μνήμη απομόνωσης (memory

buffer), υποβοηθούμενες ενίοτε από μία τοπολογία που

ονομάζεται VCXO. Ακόμη και αν έχετε στην διάθεσή

σας ένα πανάκριβο (και εξαιρετικά αποτελεσματικό) σύστημα, οι

πιθανότητες είναι στο εσωτερικό του να κρύβεται κάτι από όλα

αυτά. |

| Το

PLL (Phase Locked Loop): H ιστορία του διπλού

εκκρεμούς... |

|

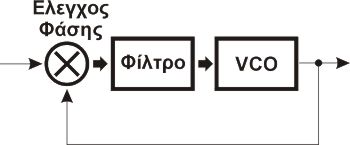

| Aπλό

διάγραμμα βαθμίδων του PLL | |

| Ως ιδέα, το PLL έχει τις ρίζες

του στο 1665, όταν ο Ολλανδός Christiaan Huygens

(προφέρεται Χόιχενς), o oποίος μεταξύ άλλων κατασκεύασε και τα πρώτα

ρολόγια με εκκρεμές, παρατήρησε ότι δύο από τα εκκρεμή του, που

βρίσκονταν σε γειτονία, έτειναν να συγχρονισθούν σε αντίθεση φάσης,

ακόμη και όταν επενέβη και άλλαξε την κίνηση ενός εκ των δύο. Πολύ

αργότερα αποδείχθηκε ότι αυτό οφείλεται σε μηχανική ενέργεια που

μεταβιβάζεται από το ένα εκκρεμές στο άλλο, όταν βρίσκονται κοντά,

μέσα από διάφορες οδούς. Το θέμα δεν είχε άμεση σχέση με τα

ηλεκτρονικά έδωσε όμως την ιδέα συχρονισμού δυο ηλεκτρικών

ταλαντωτών και αποτέλεσε έναν πολύ μακρινό πρόγονο του

ομόδυνου ραδιοφωνικού δέκτη ο οποίος ήταν και η πρώτη συσκευή που

χρησιμοποίησε το κύκλωμα που σήμερα ονομάζεται PLL. Η ομάδα των

βρετανών ερευνητών που παρουσίασε τον εν λόγω δέκτη, το

1932, ήθελε ένα κύκλωμα που να εξασφαλίζει το "κλείδωμα"

ενός ταλαντωτή που βρισκόταν μέσα στην συσκευή με την φέρουσα

συχνότητα ενός ραδιοφωνικού σταθμού ώστε να μην υπάρχει ολίσθηση

(λόγω διάφορων ατελειών του κυκλώματος που τότε δεν ήταν και

λίγες). Ο Βρόχος Κλειδωμένης Φάσης, όπως

ονομάζεται το PLL στα ελληνικά, κάνει ακριβώς αυτό: Παρακαλουθεί ένα

σήμα και ελέγχει έναν ταλαντωτή μεταβλητής συχνότητας, την έξοδο του

οποίου συγκρίνει με το σήμα στην είσοδο. Στην φάση ισορροπίας του

PLL, τα δύο σήματα (εισόδου και εξόδου) βρίσκονται σε συχρονισμό

(δηλαδή σε φάση) και αν υπάρξει κάποια ολίσθηση τότε το PLL

εφαρμόζει ένα σήμα ελέγχου που μεταβάλει την συχνότητα εξόδου έτσι

ώστε να υπάρξει και πάλι συγχρονισμός (το σήμα ελέγχου είναι συνήθως

μία τάση, γι αυτό και ο ταλαντωτής του PLL είναι ελεγχόμενος από

τάση, VCO-Voltage Controled Oscillator). Ο τρόπος με τον οποίο

ελέγχεται η συχνότητα εξόδου εξαρτάται από τις επιλογές μας: Αυτό

μπορεί να γίνεται πολύ γρήγορα ή πολύ αργά, ανάλογα με το τί θέλουμε

να επιτύχουμε. |

|

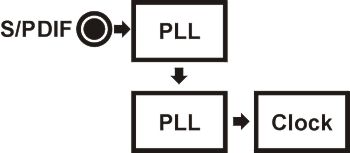

| Το πρώτο

στάδιο κάθε ψηφιακού interface είναι ένα PLL το οποίο

πραγματοποιεί clock recovery, ανακτά δηλαδή την πληροφορία

χρονισμού από το ψηφιακό

σήμα. | |

| Στην περίπτωση του clock στα

ψηφιακά συστήματα audio, αυτό που μας ενδιαφέρει είναι να επιτύχουμε

συγχρονισμό του τοπικού κυκλώματος χρονισμού με τις πληροφορίες που

περιέχονται στο σήμα (και είναι -αν θυμάστε- αγρίως παραμορφωμένες!)

αλλά ταυτόχρονα μία σχετική αδράνεια στις διακυμάνσεις λόγω

jitter, κάτι που επιτυγχάνεται με ένα "αργό" PLL. Tα

κυκλώματα κλειδωμένης φάσης είναι βασικά δομικά στοιχεία κάθε

ψηφιακού interface που σέβεται τον εαυτό του. Μάλιστα στο σημείο

αυτό (του PLL δηλαδή) γίνεται ένα ακόμη παιχνίδι όσον αφορά

στο clock recovery: Αντί το κύκλωμα να παρακολουθεί το ίδιο

το σήμα για να εξάγει το clock (θυμάστε; Υπάρχει ένα jitter που

εξαρτάται από την μορφή του σήματος και θα θέλαμε να το αποφύγουμε!)

παρακολουθεί τις διακοπές που εισάγονται ανάμεσα στις λέξεις που

περιγράφουν τα δεδομένα για κάθε κανάλι, οι οποίες είναι μεγαλύτερες

σε διάρκεια (επομένως η γραμμή μεταφοράς μας συμπεριφέρεται καλύτερα

στιγμιαία!). H τεχνική εμφανίζεται με διάφορα ονόματα αλλά η κλασική

της ονομασία είναι preamble clock

recovery. |

|

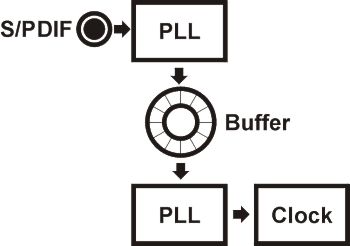

| Clock με

διπλό PLL: Το πρώτο στάδιο ανακτά το clock από το ψηφιακό σήμα

και το δεύτερο στάδιο σταθεροποιεί ακόμη περισσότερο το σήμα

χρονισμού. | |

|

|

| Τελειώσαμε με το jitter; Oχι

βέβαια! Η έξοδος του PLL έχει κι αυτή ένα ποσοστό

διακύμανσης (μην ξεχνάτε ότι παρακολουθεί την είσοδο, έστω

και με αδράνεια) αλλά πολύ μικρότερο. Το αν αυτό είναι αποδεκτό,

εξαρτάται από το επίπεδο της συσκευής και το ποσοστό του συνολικού

κόστους που μπορεί να δαπανηθεί σε αυτό το σημείο. Αν τα λογιστικά

μάς το επιτρέπουν μπορούμε να χρησιμοποιήσουμε ένα δεύτερο

PLL το οποίο θα χρησιμοποιεί ως είσοδο, την έξοδο του

πρώτου, για να δημιουργήσει ένα clock με ακόμη μικρότερη διακύμανση.

Και το επόμενο βήμα (όταν ο οικονομικός διευθυντής βρίσκεται σε

διακοπές κάπου στο νότιο ημισφαίριο) θα είναι να

παρεμβάλουμε μία μνήμη ανάμεσα στα δύο PLL η οποία θα

τροφοδοτείται από την έξοδο τους πρώτου και θα τροφοδοτεί την είσοδο

του δεύτερου. |

|

| Clock

recovery με διπλό PLL και μνήμη απομόνωσης. Η μνήμη

είναι συνήθως FIFO (First In, First Out) και επιτρέπει την

διόρθωση jitter με μεγάλη χρονική

διακύμανση. | |

| Η χωρητικότητα της μνήμης

αυτής καθορίζει "πόσο χαμηλά μπορεί να κατέβει" το σύστημά μας στην

καταστολή του jitter. Οσο μεγαλύτερη, τόσο πιο αργές μεταβολές του

χρονισμού μπορεί να διορθωθούν, επειδή μπορούν να αποθηκευθούν

μεγαλύτερα μέρη του σήματος. Τέλος, η ποιότητα του ταλαντωτή που

χρησιμοποιήται σε κάθε PLL είναι σημαντική. Η καλύτερη επιλογή εδώ

είναι οι VCXO (Voltage Controled Crystal

Oscillators) oι οποίοι χρησιμοποιούν έναν κρύσταλλο για τον

καθορισμό της βασικής τους συχνότητας με πολύ μεγάλη ακρίβεια

(αν θέλει κάποιος να είναι παρανοικά ακριβής,

μπορεί να βάλει τον κρύσταλλο και σε φούρνο, για να διατηρεί σταθερή

την θερμοκρασία του... μία επιλογή που χρησιμοποιήται σε συσκευές

μεγάλης ακρίβειας όπως είναι τα όργανα μετρήσεων). Το μειονέκτημα

αυτής της προσέγγισης είναι ότι ένας τέτοιος, κρυσταλλικά

ελεγχόμενος ταλαντωτής δεν μπορεί να παρακολουθήσει μεγάλες αλλαγές

συχνότητας επομένως χρειάζεται ένας κρύσταλλος για κάθε sampling

rate στο οποίο θα κλειδώνει το PLL και για τον λόγο αυτό τέτοιου

είδους λύσεις συναντώνται μόνο σε σχετικώς ακριβά

συστήματα. |

Για περισσότερο

διάβασμα:

1.

Digital Audio Design Seminar, Robert Watson, Richard Kulavic,

Βurr-Brown

2. Towards Common Specifications for Digital Audio

Interface Jitter, Julian Dunn et al,

3. The Diagnosis and

Solution of Jitter-Related problems in Digital Audio Systems, Julian

Dunn, Ian Dennis, AES Preprint, 96th Convention, 1994

4. Jitter:

Specification and Assesment in Digital Audio Equipment, Julian Dunn,

AES Preprint, 93rd Convention, 1992

5. Jitter in Clock Sources,

Joe Adler, http://www.vectron.com/

6. Timing Errors and Jitter, Mike Story,

dCS White Paper 10/1998

7. DIGITabilis crash course on digital

audio interfaces, http://www.tnt-audio.com/

8. Discrete-Time Signal Processing, Oppenheim/Schafer,

Prentice Hall, 1989

9. Convergence in Broadcastand Communications

Media, Watkinson, Focal Press, 2001 |

|

| |